# A 5–10 GHz 15-W GaAs MESFET Amplifier with Flat Gain and Power Responses

Yasushi Itoh, *Senior Member, IEEE*, Mitsuru Mochizuki, Masaki Kohno, Hiroyuki Masuno, Tadashi Takagi, *Member, IEEE*, and Yasuo Mitsui, *Member, IEEE*

**Abstract**— A 5–10 GHz 15-W GaAs MESFET amplifier has been developed. It utilizes a multisection maximally flat impedance transformer whose length is designed to become a quarter wavelength at the highest frequency of the design band to achieve flat gain and flat power responses over a wide bandwidth. With the use of this transformer, the amplifier has achieved a linear gain of  $9 \pm 1$  dB, a  $P_1$  dB of  $41.8 \pm 1$  dBm, and a power-added efficiency of  $27.5 \pm 7.5\%$  over 5–10 GHz, which demonstrate the highest power-bandwidth product ever achieved by high-power amplifiers using GaAs MESFET's, PHEMT's or HBT's.

## I. INTRODUCTION

**I**N RECENT microwave communication and measurement systems, traveling-wave tube amplifiers (TWTA's) are being replaced by solid-state power amplifiers (SSPA's) because SSPA's have a number of advantages over TWTA's, including small size, light weight, and high reliability [1], [2]. In the design of SSPA's, a quarter-wavelength impedance transformer [3] has been used as an impedance matching and transforming network. The conventional high-power amplifiers have chosen the length of an impedance transformer at a quarter wavelength at the center frequency of the design band [4], [5]. This design method, however, provides a serious problem when applied to the design of wideband high-power amplifiers. The gain and power decrease drastically at the highest frequency of the design band because a perfect match is obtained only at the center frequency of the design band. In addition, the gain and power decrease as the frequency increases. To overcome this problem, we employed a design method to utilize a multisection maximally flat impedance transformer whose length is chosen as a quarter wavelength at the highest frequency of the design band. The feature of this design is in that flat gain and flat power can be obtained by optimizing the number of sections of the input and output impedance transformers to compensate for the frequency-dependent gain and power slopes.

## II. CIRCUIT DESIGN

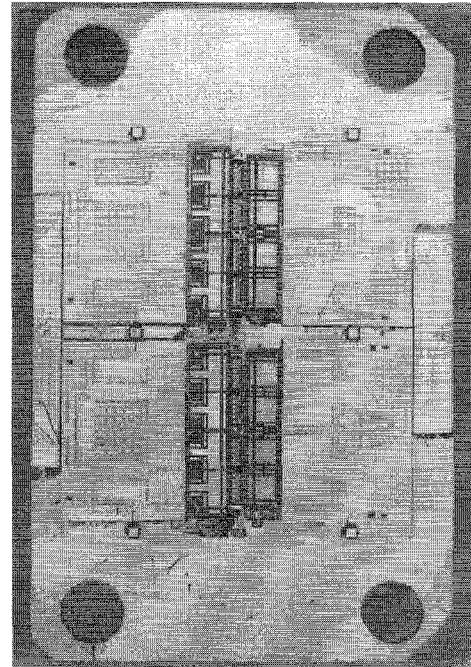

A photograph of the 5–10 GHz high-power amplifier is shown in Fig. 1. In order to achieve a linear gain of 8 dB

Fig. 1. Photograph of the 5–10 GHz high-power amplifier.

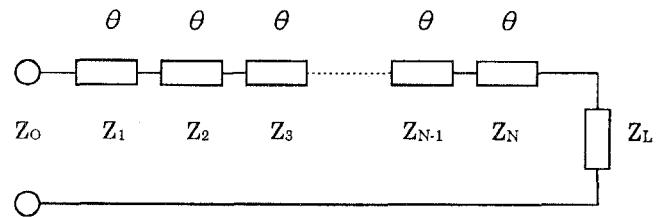

Fig. 2. Simplified schematic diagram of the multisection quarter-wave impedance transformer.

and a 1-dB compressed power greater than 40 dBm over 5–10 GHz, eight GaAs MESFET's with a gate periphery of 5.25 mm were combined in parallel. The input and output matching networks employ a multisection impedance transformer. A simplified schematic diagram of the multisection quarter-wave impedance transformer is shown in Fig. 2, where  $\theta$  is the electrical length,  $Z_0$  and  $Z_L$  are the source and load impedance, and  $N$  is the number of sections. To achieve flat gain and flat power of the amplifier, a maximally flat impedance transformer that does not show any ripples as the frequency changes is employed. The length  $\theta$  is chosen at a quarter wavelength at the highest frequency (10 GHz) of

Manuscript received July 14, 1995.

Y. Itoh, T. Takagi, and Y. Mitsui are with the Electro-Optics and Microwave Systems Laboratory, Mitsubishi Electric Corporation, Kanagawa 247, Japan.

M. Mochizuki and H. Masuno are with the Communication Equipment Works, Mitsubishi Electric Corporation, Hyogo 661, Japan.

M. Kohno is with the Kitatami Works, Mitsubishi Electric Corporation, Hyogo 664, Japan.

IEEE Log Number 9415378.

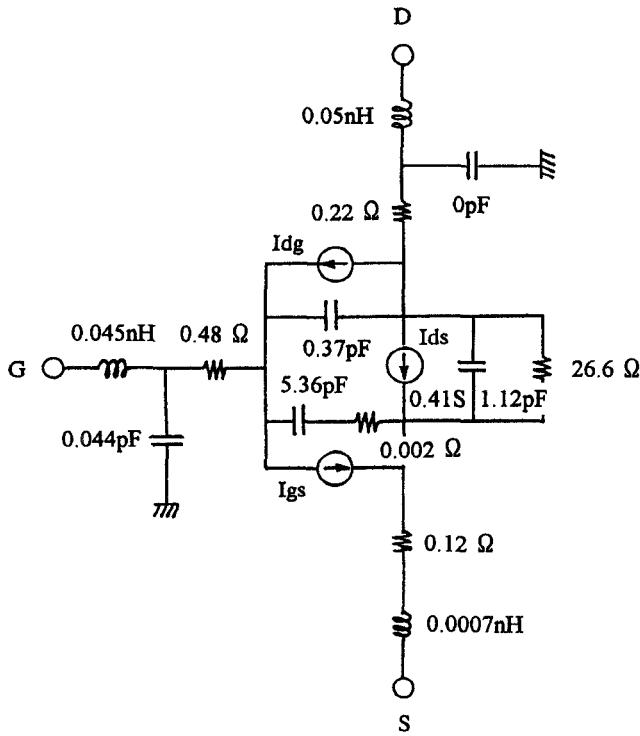

Fig. 3. Large-signal FET model of the 5.25-mm FET.

TABLE I

HIGH DIELECTRIC SUBSTRATE EMPLOYED IN THE INPUT MATCHING NETWORK

| substrate           | transformer | $Z_1, Z_2$ | $Z_3, Z_4, Z_5, Z_6$ | $Z_7$ |

|---------------------|-------------|------------|----------------------|-------|

| dielectric constant |             | 9.8        | 9.8                  | 38    |

| thickness           |             | 0.635      | 0.2                  | 0.18  |

TABLE II

HIGH DIELECTRIC SUBSTRATE EMPLOYED IN THE OUTPUT MATCHING NETWORK

| substrate           | transformer | $Z_1, Z_2$ | $Z_3, Z_4, Z_5$ | $Z_6, Z_7$ |

|---------------------|-------------|------------|-----------------|------------|

| dielectric constant |             | 9.8        | 9.8             | 89         |

| thickness           |             | 0.38       | 0.2             | 0.15       |

the design band. The number of sections ( $N$ ) was determined by using the following approach. First, for achieving a flat power of the amplifier, the number of sections of the output matching network is determined to compensate for the frequency-dependent power characteristics of FETs based on load-pull measurements. Second, for achieving a flat gain of the amplifier, the number of sections of the input matching network is determined to compensate for the frequency-dependent gain characteristics of FETs based on small-signal  $S$ -parameter measurements. In the design of impedance transformers,  $Z_O$  is  $50 \Omega$  and  $Z_L$  is assumed to be real and positive. For the input matching network,  $Z_L$  is determined as the sum of the gate resistance ( $R_g$ ), the gate-to-source resistance ( $R_i$ ), and the source resistance ( $R_s$ ) of eight GaAs MESFET's with a gate periphery of 5.25 mm,

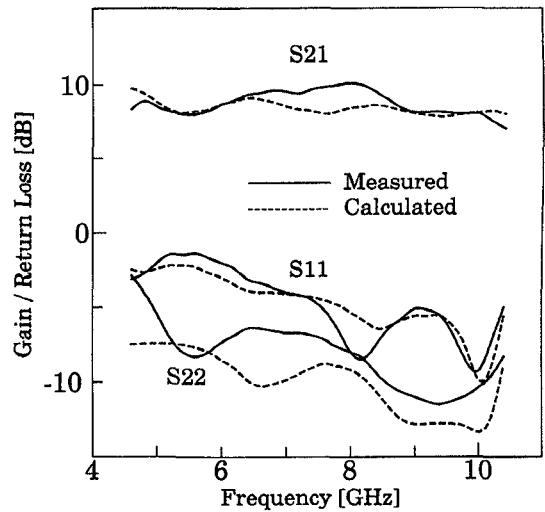

Fig. 4. Measured and calculated gain and return loss.

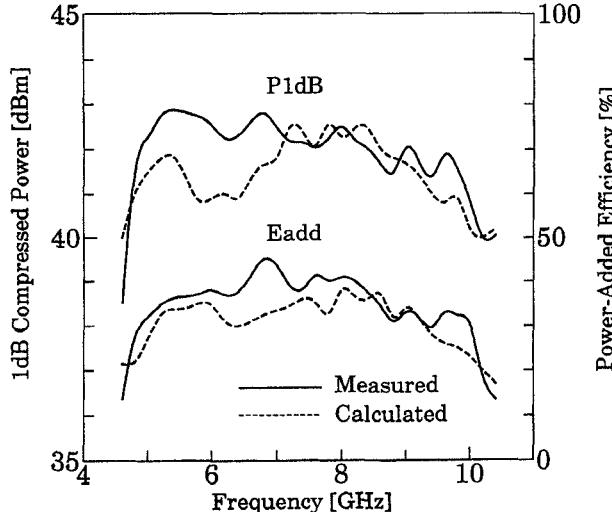

Fig. 5. Measured and calculated 1-dB compressed power and power-added efficiency.

whose large-signal FET model is shown in Fig. 3. The large-signal FET model is based on the curtice cubic model [6]. For the output matching network,  $Z_L$  is determined as the drain-to-source resistance ( $R_{ds}$ ) under large-signal operation, which has been obtained from the load-pull measurements and large-signal FET model. The value of  $Z_L$  was  $0.075 \Omega$  for the input matching network and  $1.32 \Omega$  for the output matching network [7]. The number of sections of impedance transformers was determined to be 7 for both input and output matching networks.

The 7-section impedance transformers are required to play a role of power splitting and combining circuits because eight GaAs FET's have to be combined in parallel. Thus each transformer is designed to employ a tournament structure shown in Fig. 1. The circuit parameters shown in Fig. 1 were optimized to show a linear gain of 8 dB and a 1-dB compressed power greater than  $40 \text{ dBm}$  over 5–10 GHz by using the large-signal FET model shown in Fig. 3 and the harmonic balance method. The final length of each impedance transformer was

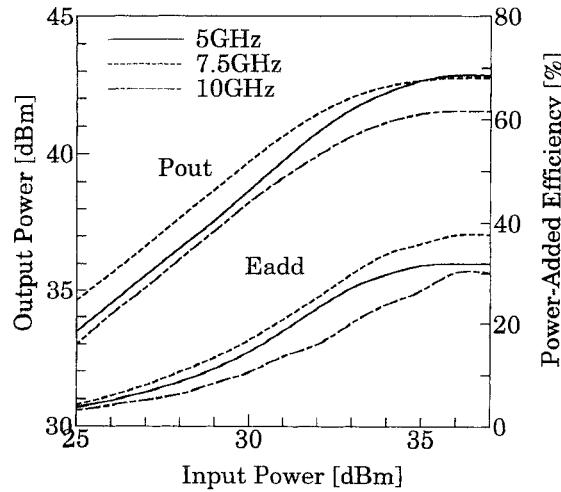

Fig. 6. Measured transfer characteristics.

a quarter wavelength at around 15 GHz. This is probably due to the fact that the input and output impedance of FET's does not show a pure resistance, as shown in Fig. 3.

### III. FABRICATION AND PERFORMANCE

Both input and output impedance transformers were fabricated on high dielectric substrates shown in Tables I and II by using thin-film circuits. The circuits employ several isolation resistors to remove the loop oscillation in a closed-loop circuit due to the imbalance between FET's. Two 5.25-mm FET's are fabricated on the same FET chip to keep the imbalance of dc and rf performance between FET's small. The size of the amplifier is  $14 \times 17$  mm<sup>2</sup>.

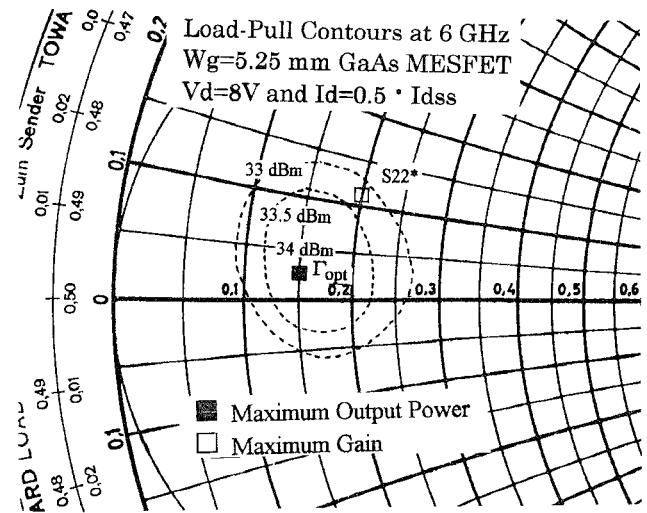

The measured and calculated gain and return loss are plotted in Fig. 4. The measured gain is  $9 \pm 1$  dB over 5–10 GHz. The measured and calculated results for both gain and return loss are in good agreement. It is clear in Fig. 4 that a mismatch in the input and output matching networks becomes larger as the frequency decreases. This mismatch will be improved by employing a balanced configuration with quadrature couplers. The measured and calculated 1-dB compressed power and power-added efficiency are  $41.8 \pm 1$  dBm and  $37.5 \pm 7.5\%$  across 5–10 GHz, respectively. Some discrepancy between the measured and calculated results for power appears from 5–7 GHz. This is probably due to some errors in the model parameters of FET's. The 5.25 mm FET has shown a P1 dB from 34.0–34.2 dBm by the load-pull measurements for the design band. The measured load-pull contours at 6 GHz are shown in Fig. 7. Taking into account this load-pull data, a mismatch loss or circuit loss ranges from 1.2–1.4 dB as an averaged value. The data shown in Figs. 4–7 were measured at a drain voltage of 8 V and a drain current of  $0.5 \cdot I_{dss}$ . No circuit tuning was employed to achieve flat gain and power responses over a wide bandwidth.

Fig. 7. Measured load-pull contours.

### IV. CONCLUSION

A 5–10 GHz 15-W GaAs MESFET amplifier has been developed by using a multisection maximally flat impedance transformer whose length is chosen to become a quarter wavelength at the highest frequency of the design band to achieve flat gain and flat power over a wide bandwidth. With the use of this transformer, the amplifier has achieved a linear gain of  $9 \pm 1$  dB, a 1-dB compressed power of  $41.8 \pm 1$  dBm, and a power-added efficiency of  $37.5 \pm 7.5\%$  over 5–10 GHz. This amplifier demonstrates the highest power-bandwidth product ever achieved by high-power amplifiers using GaAs MESFET's, PHEMT's or HBT's. This performance would be improved by using GaAs PHEMT's or HBT's with better gain and power performance.

### REFERENCES

- [1] M. Salib, F. Ali, A. Gupta, B. Bayraktaroglu, and D. Dawson, "A 5–10 GHz, 1-Watt HBT amplifier with 58% peak power-added efficiency," *IEEE Microwave and Guided Wave Lett.*, vol. 4, no. 10, pp. 320–322, Oct. 1994.

- [2] J. J. Komiak, "Octave band eleven watt power amplifier MMIC," in *1990 IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp. Dig.*, 1990, pp. 35–38.

- [3] R. E. Collin, "Foundations for microwave engineering," in *McGraw-Hill International Editions*, 1966.

- [4] Y. Ikeda, T. Takagi, H. Hirose, and S. Urasaki, "C-band high efficiency GaAs FET amplifier with 17.4 W output power," in *Proc. 20th European Microwave Conf.*, 1990, pp. 307–309.

- [5] S. Tsuji, K. Seino, S. Sakamoto, T. Sakayori, T. Takagi, M. Yamanouchi, S. Takamiya, and Y. Kashimoto, "13 watts power GaAs FET for 14.0–14.5 GHz band," in *Proc. 3rd Asia-Pacific Microwave Conf.*, 1990, pp. 537–539.

- [6] W. R. Curtice and M. Ettenberg, "A nonlinear GaAs FET model for use in the design of output circuits for power amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, no. 12, pp. 1383–1394, Dec. 1985.

- [7] M. Mochizuki, Y. Itoh, M. Kohno, H. Masuno, and T. Takagi, "C-X band 14 W power amplifier having flat gain and power response," in *1993 IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 1365–1368.